最近在圣克拉拉举行的开放创新平台生态系统论坛上,台积电(TSMC)对异构封装的未来进行了展望。尽管Chiplet packaging经常被用来描述具有潜在广泛变化功能的多个硅芯片的集成,但本文将使用“异构封装”来代表它。下面的示例说明了大裸片和小裸片、DRAM裸片以及全高带宽内存裸片堆栈(HBM2)的集成,比通常“chiplet”的范围要丰富得多。台积电集成互连与封装副总裁Douglas Yu博士介绍了当前台积电异构封装产品,提出了3D封装的发展,并将之形容为“More-than-More-than-Moore”。

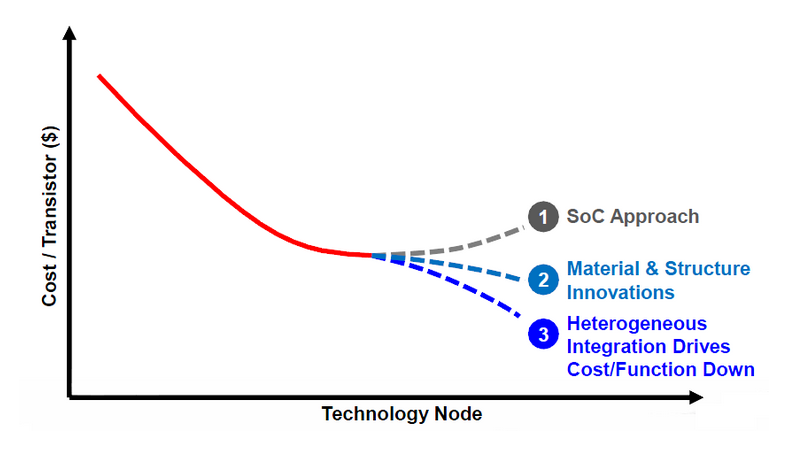

Douglas表示随着集成电路工艺技术的发展,晶体管的单位成本提高的速度已经放缓。图1.随着工艺技术的升级,晶体管单位成本的提高速度已经放缓。(来源:台积电)

扩大规模肯定会带来持续的产品PPA(Performance,Power,Area)收益,但是整个系统功能的最终成本可能会驱使系统设计人员寻求异构封装的替代方案。

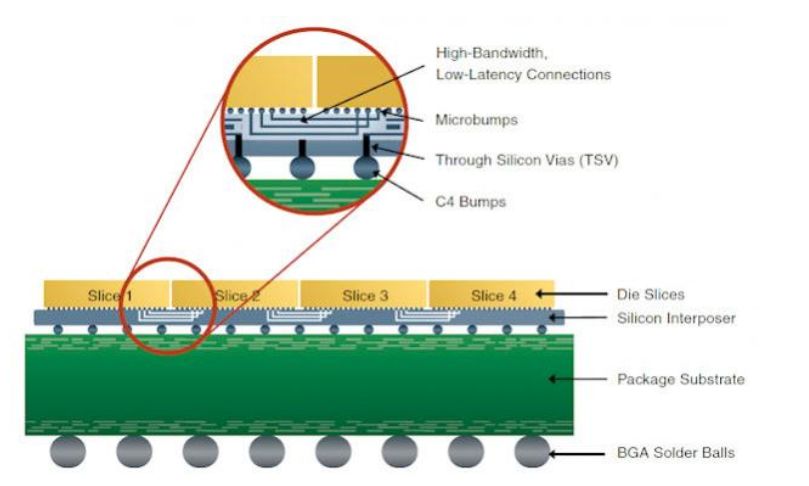

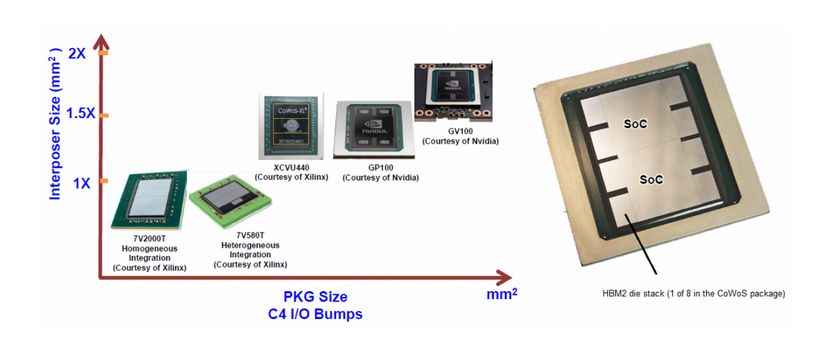

台积电提供的首款异质封装产品是基板上晶圆上芯片封装(CoWoS®)。封装的横截面如下图所示。

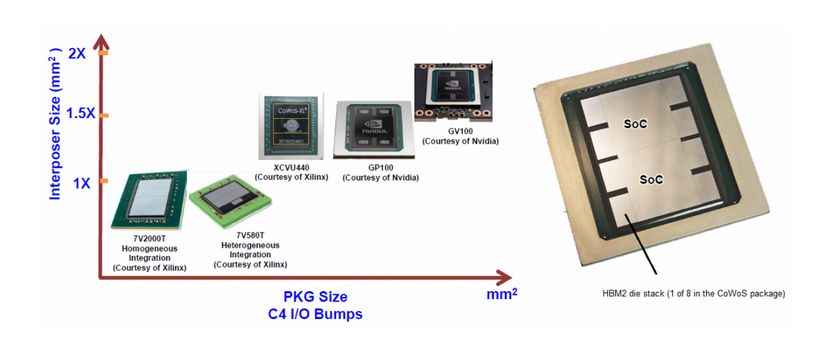

硅中介层提供了die之间的互连,并通过硅通孔(TSV)连接到下面的基板。Douglas介绍了CoWoS®技术在生产中的最新进展,特别是能够为晶圆光刻以最大光罩尺寸的2倍来制造中介层。

图3.CoWo®S对硅中介层的支持大于单个最大光罩尺寸(来源:TSMC)

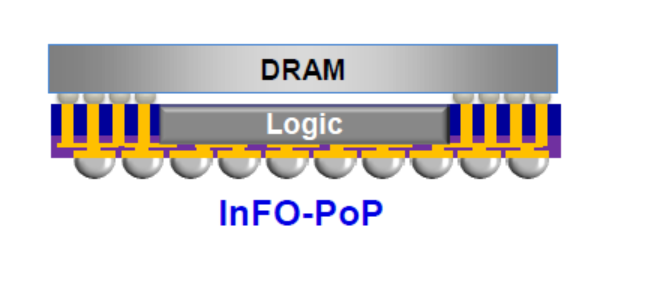

Douglas回顾了台积电基于Integrated Fanout(Info)技术的异构封装。原始的Info 产品提供了(重构的)晶圆级重新分布层连接到裸片外围之外的扩展凸块位置。下面展示了较新的Info POP封装截面。

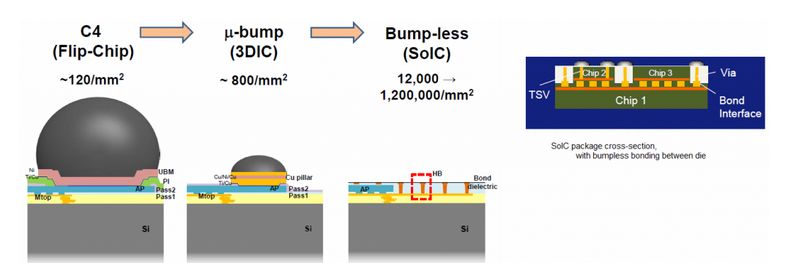

Info 模压封装超出嵌入式管芯,还可用于顶部管芯和再分布层连接之间的Through-InFO vias(TIV)。台积电(TSMC)异构封装的最新创新涉及从管芯和基板之间的微凸点连接过渡到直接管芯连接之间的无凸点(热压)键合的转变–有关微凸点和无凸点连接之间的比较,请参见下图。TSMC-SoIC®是一个创新的基于晶圆工艺的前端平台,集成了多芯片,多层,多功能和混合匹配技术,可实现高速,高带宽,低功耗,高音调密度和最小的占位面积和堆叠高度的异构3D IC集成。图5.凸点和无凸点技术特性与SOIC®封装截面的比较(来源:TSMC)

硅通孔提供了与凸点的连接,这是最终后端封装组装流程的一部分。无凸点附着技术的密度和电气特性要优越得多。Douglas提出了一个异种封装的设想,它结合了上述技术的独特优势。下图直接描绘了SOIC®复合封装将成为Info®或Cowos®封装的一部分,可以集成了更多的die和HBM内存栈。

下第二幅图说明了使用无凸点连接进行后续后端封装组装的多层(薄型)管芯。Douglas将此多层SOIC®解决方案称为从3D系统集成向全3D系统扩展过渡的一部分。图6.SOIC®集成到后续的info或Cowos®封装中(来源:TSMC)

图7.多层无凸点芯片集成 à3D系统缩放(来源:TSMC)

由TSMC提出的异构封装技术愿景将真正为系统架构师提供持续扩展的巨大机会。除了传统的单片芯片PPA技术选择考虑因素之外,这一愿景还为系统级功能集成和封装成本优化提供了额外的机会。看看这些异构封装产品如何影响未来的系统设计将非常有趣。(文章来源:半导体行业观察)